I am officially joining the Department of Electrical and Computer Engineering at the University of Washington (UW ECE) as an assistant professor in 2023 fall! Super excited for the journey ahead!

About Me

I am a final-year Ph.D. candidate in the ECE department, Princeton University. I am supervised by Prof. David Wentzlaff who leads the Princeton Parallel Group.

I am interested in all aspects of computer architecture and digital VLSI design, especially heterogeneous and reconfigurable systems for both high-performance and low-power applications. I enjoy building chips so as to validate and evaluate my ideas with high fidelity. I am also an advocate of open-source hardware/research as they increase research credibility/reproducibility and encourage community-wide collaboration.

Latest News

- 06/18/23 Yanwen gave a virtual talk on Redwood at OSCAR’23.

- 06/18/23 I gave a talk about our silicon prototypes of PRGA at OSCAR’23.

- 04/25/23 Fei presented DECADES at CICC’23! Great job!

- 04/25/23 I presented CIFER at CICC’23!

- 04/25/23 Yanwen presented Redwood at ISPASS’23! Great job!

- 02/28/23 August presented Duet at HPCA’23! Great job!

- 02/28/23 Our paper on programming/benchmarking shared-memory heterogeneous systems (CPU-GPU/CPU-FPGA), Redwood, is accepted to ISPASS’23! Congrats, Yanwen and Tyler!

- 01/16/23 Media coverage of Duet by Semiconductor Engineering and Acceleration Robotics!

- 01/13/23 Our paper on CIFER is accepted to CICC’23!

- 01/13/23 Our paper on DECADES is accepted to CICC’23!

Projects

PRGA - Princeton Reconfigurable Gate Array

A silicon-proven, open-source project for generating customized, synthesizable FPGA with complementary, RTL-to-bitstream CAD toolchain.

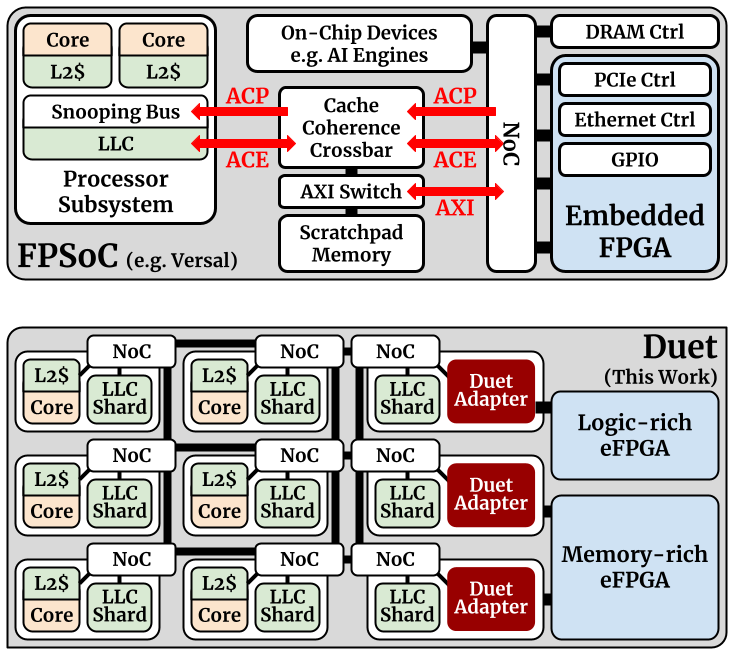

Duet - Harmonious CPU-FPGA Integration

A novel approach to integrate manycores and multiple eFPGA fabrics to exploit fine-grained acceleration opportunities in the broad application domain.

- Duet has been published and presented at HPCA'23!

- Media coverage by Semiconductor Engineering and Acceleration Robotics!

gem5 x Duet

A gem5 extension for simulating tightly-integrated, ASIC or FPGA-based accelerators. Gem5-Duet achieves C/C++-level simulation speed with cycle-level accuracy by compiling the High-Level Synthesis (HLS) source code into the simulator and applying post-HLS timing annotation in the runtime configuration script.

CIFER

A heterogeneous, cache-coherent, manycore-eFPGA SoC. CIFER integrates OS-capable cores, parallel tiny core clusters, and eFPGA fabrics in a coherent cache system, covering both ends of the parallelization-specialization spectrum.

- In collab with Prof. Christopher Batten's group

- Prototype chip fabricated and tested

- CIFER has been published and presented at CICC'23!

DECADES

A heterogeneous, cache-coherent SoC with processors, specialized accelerators, intelligent storage units, and eFPGAs. The project is part of an effort to create hardware and software that can be reconfigured on the fly to accelerate important applications.

- In collab with Prof. Margaret Martonosi's group

- In collab with Prof. Luca Carloni's group

- Prototype chip fabricated and tested

- DECADES has been published and presented at CICC'23!

ORDER

ORDER is a microcontroller-eFPGA SoC designed with fully open-source hardware projects (Caravel and PRGA), PDK (SkyWater130), and EDA toolchain (OpenROAD).

- Selected for OpenMPW-6. Fabrication in progress.

Referred Publications | Full List

Redwood: Flexible and Portable Heterogeneous Tree Traversal Workloads

@INPROCEEDINGS{10158162,

author={Xu, Yanwen and Li, Ang and Sorensen, Tyler},

booktitle={2023 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS)},

title={{Redwood: Flexible and Portable Heterogeneous Tree Traversal Workloads}},

year={2023},

volume={},

number={},

pages={201-213},

doi={10.1109/ISPASS57527.2023.00028}}

2023 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), April 2023, Raleigh, NC, USA

CIFER: A 12nm, 16mm2, 22-Core SoC with a 1541 LUT6/mm2, 1.92 MOPS/LUT, Fully Synthesizable, Cache-Coherent, Embedded FPGA

@INPROCEEDINGS{10121294,

author={Chang, Ting-Jung and Li, Ang and Gao, Fei and Ta, Tuan and Tziantzioulis, Georgios and Ou, Yanghui and Wang, Moyang and Tu, Jinzheng and Xu, Kaifeng and Jackson, Paul J. and Ning, August and Chirkov, Grigory and Orenes-Vera, Marcelo and Agwa, Shady and Yan, Xiaoyu and Tang, Eric and Balkind, Jonathan and Batten, Christopher and Wentzlaff, David},

booktitle={2023 IEEE Custom Integrated Circuits Conference (CICC)},

title={{CIFER: A 12nm, 16mm2, 22-Core SoC with a 1541 LUT6/mm2 1.92 MOPS/LUT, Fully Synthesizable, CacheCoherent, Embedded FPGA}},

year={2023},

volume={},

number={},

pages={1-2},

doi={10.1109/CICC57935.2023.10121294}}

2023 IEEE Custom Integrated Circuits Conference (CICC), April 2023, San Antonio, TX, USA

DECADES: A 67mm2, 1.46TOPS, 55 Giga Cache-Coherent 64-bit RISC-V Instructions per second, Heterogeneous Manycore SoC with 109 Tiles including Accelerators, Intelligent Storage, and eFPGA in 12nm FinFET

Best Student Paper Nominee

@INPROCEEDINGS{10121257,

author={Gao, Fei and Chang, Ting-Jung and Li, Ang and Orenes-Vera, Marcelo and Giri, Davide and Jackson, Paul J. and Ning, August and Tziantzioulis, Georgios and Zuckerman, Joseph and Tu, Jinzheng and Xu, Kaifeng and Chirkov, Grigory and Tombesi, Gabriele and Balkind, Jonathan and Martonosi, Margaret and Carloni, Luca and Wentzlaff, David},

booktitle={2023 IEEE Custom Integrated Circuits Conference (CICC)},

title={{DECADES: A 67mm2, 1.46TOPS, 55 Giga Cache-Coherent 64-bit RISC-V Instructions per second, Heterogeneous Manycore SoC with 109 Tiles including Accelerators, Intelligent Storage, and eFPGA in 12nm FinFET}},

year={2023},

volume={},

number={},

pages={1-2},

doi={10.1109/CICC57935.2023.10121257}}

2023 IEEE Custom Integrated Circuits Conference (CICC), April 2023, San Antonio, TX, USA

Duet: Creating Harmony between Processors and Embedded FPGAs

@INPROCEEDINGS{10070989,

author={Li, Ang and Ning, August and Wentzlaff, David},

booktitle={2023 IEEE International Symposium on High-Performance Computer Architecture (HPCA)},

title={{Duet: Creating Harmony between Processors and Embedded FPGAs}},

year={2023},

volume={},

number={},

pages={745-758},

doi={10.1109/HPCA56546.2023.10070989}}

The 29th IEEE International Symposium on High-Performance Computer Architecture (HPCA), Feb-Mar 2023, Montreal, QC, Canada

PRGA: An Open-Source FPGA Research and Prototyping Framework

DOI Bibtex PDF Recorded Presentation GitHub Website Documentation

@inproceedings{10.1145/3431920.3439294,

author = {Li, Ang and Wentzlaff, David},

title = {{PRGA: An Open-Source FPGA Research and Prototyping Framework}},

year = {2021},

isbn = {9781450382182},

publisher = {Association for Computing Machinery},

address = {New York, NY, USA},

url = {https://doi.org/10.1145/3431920.3439294},

doi = {10.1145/3431920.3439294},

abstract = {Field Programmable Gate Arrays (FPGA) are being used in a fast-growing range of scenarios, and heterogeneous CPU-FPGA systems are being tapped as a possible way to mitigate the challenges posed by the end of Moore's Law. This growth in diverse use cases has fueled the need to customize FPGA architectures for particular applications or application domains. While high-level FPGA models can help explore the FPGA architecture space, as FPGAs move to more advanced design nodes, there is an increased need for low-level FPGA research and prototyping platforms that can be brought all the way to fabrication.This paper presents Princeton Reconfigurable Gate Array (PRGA), a highly customizable, scalable, and complete open-source framework for building custom FPGAs. The framework's core functions include generating synthesizable Verilog from user-specified FPGA architectures, and providing a complete, auto-generated, open-source CAD toolchain for the custom FPGAs. Developed in Python, PRGA provides a user-friendly API and supports use both as a standalone FPGA as well as an embedded FPGA. PRGA is a great platform for FPGA architecture research, FPGA configuration memory research, FPGA CAD tool research, and heterogeneous systems research. It is also a completely open-source framework for designers who need a free and customizable FPGA IP core. An FPGA designed with PRGA is placed and routed using standard cell libraries. The design is evaluated and compared to prior works, providing comparable performance and increased configurability.},

booktitle = {The 2021 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays},

pages = {127–137},

numpages = {11},

keywords = {FPGA architecture, open-source hardware, FPGA},

location = {Virtual Event, USA},

series = {FPGA '21}

}

The 29th ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA), Feb-Mar 2021, Virtual

Automated Design of FPGAs Facilitated by Cycle-Free Routing

@INPROCEEDINGS{9221519,

author={Li, Ang and Chang, Ting-Jung and Wentzlaff, David},

booktitle={2020 30th International Conference on Field-Programmable Logic and Applications (FPL)},

title={{Automated Design of FPGAs Facilitated by Cycle-Free Routing}},

year={2020},

volume={},

number={},

pages={208-213},

doi={10.1109/FPL50879.2020.00042}}

The 30th International Conference on Field-Programmable Logic and Applications (FPL), Aug-Sep 2020, Virtual

Teaching

- Teaching Assistant, ECE 462/562 (also COS 462), Design of Very Large-Scale Integrated (VLSI) Systems, 2022 Fall

- Teaching Assistant, ECE 475/575 (also COS 475), Computer Architecture, 2018 Fall

- FOSSi Mentor, Google Summer of Code, 2020 Summer

- Ansh Puvvada, Automating hardware and bitstream verification for PRGA with cocotb

- Co-Advisory of Undergraduate Research

- Jaebyoek Yoon, Architecture and Physical Design of Specialized FPGAs

- Marlon Escobar, CPU-FPGA Integration

- Kevin Liu, Creating Multimode Logic Elements for a Reconfigurable Gate Array